同步时序原理简介

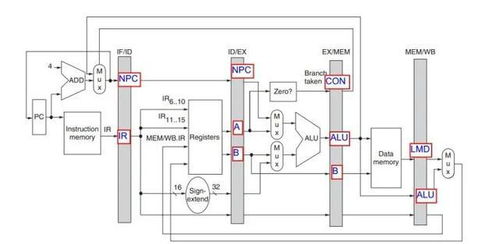

同步时序电路是数字集成电路设计的核心概念之一,其基本原理在于所有时序元件的状态更新都受控于一个全局的时钟信号。在同步时序电路中,时钟信号作为统一的时序参考,确保电路中的各个部分在特定的时间点(通常是时钟边沿)同步地进行状态转换和数据传输。

同步时序设计的关键优势在于它能有效避免竞争冒险和时序紊乱问题。通过将复杂的异步交互转化为在时钟控制下的有序操作,电路的行为变得可预测且易于分析。典型的同步时序元件包括触发器(如D触发器、JK触发器等),它们在时钟边沿到来时采样输入信号并更新输出状态。

在设计同步时序电路时,必须满足建立时间和保持时间的要求,以确保数据的正确采样。建立时间指的是数据在时钟边沿之前必须保持稳定的最小时间,而保持时间则是数据在时钟边沿之后仍需保持稳定的最小时间。违反这些时序约束可能导致亚稳态,进而引发系统故障。

同步时序原理构成了现代数字系统(如微处理器、存储器、数字信号处理器等)的设计基础,通过严格的时钟域控制和时序分析,实现了复杂功能的高可靠集成。

如若转载,请注明出处:http://www.kclgames.com/product/61.html

更新时间:2026-02-24 18:19:17