超大规模集成电路设计中的MOS器件原理(三)—— 从原理到设计的桥梁

在超大规模集成电路的设计长河中,金属-氧化物-半导体场效应晶体管是构筑现代数字与模拟电路的基石。前文已详述其基本结构与工作原理,本篇将聚焦于MOS器件原理如何深度驱动并约束超大规模集成电路的设计,探讨从微观物理到宏观系统设计的核心纽带。

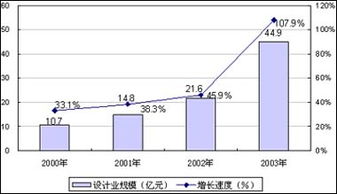

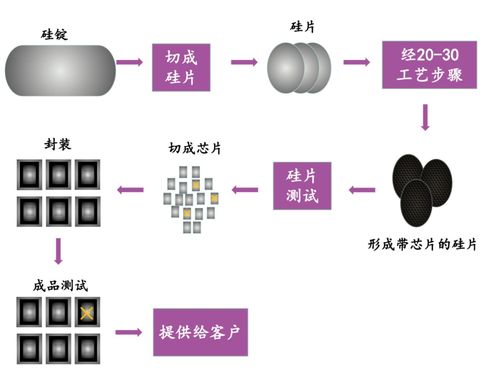

一、器件尺寸微缩:驱动设计革新的核心引擎

MOS器件的持续微缩是超大规模集成电路发展的核心动力,遵循着摩尔定律的轨迹。随着沟道长度进入纳米尺度,短沟道效应愈发显著,如阈值电压下降、漏致势垒降低等。这些物理效应直接转化为设计约束:

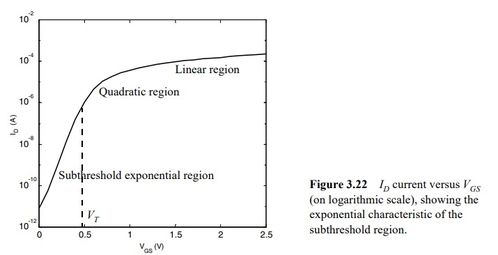

- 静态功耗挑战:亚阈值漏电流指数级增长,使得静态功耗成为芯片功耗的主要部分。设计时必须采用多阈值电压技术、电源门控等低功耗设计方法。

- 性能变异加剧:工艺波动导致器件参数(如阈值电压、沟道长度)的随机性分布加剧,直接影响电路的速度与可靠性。这要求设计流程必须纳入统计静态时序分析和良率优化。

二、工作区域与电路设计策略的对应

MOS器件的三个经典工作区域——截止区、线性区、饱和区,分别对应了数字与模拟电路的不同功能模块:

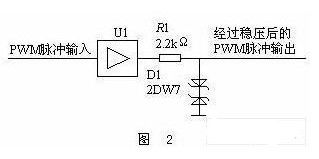

- 截止区与饱和区:构成了数字CMOS电路静态工作的基础。互补的NMOS和PMOS通过一管截止、一管饱和,实现逻辑门的“0”和“1”输出,并获得极低的静态功耗。

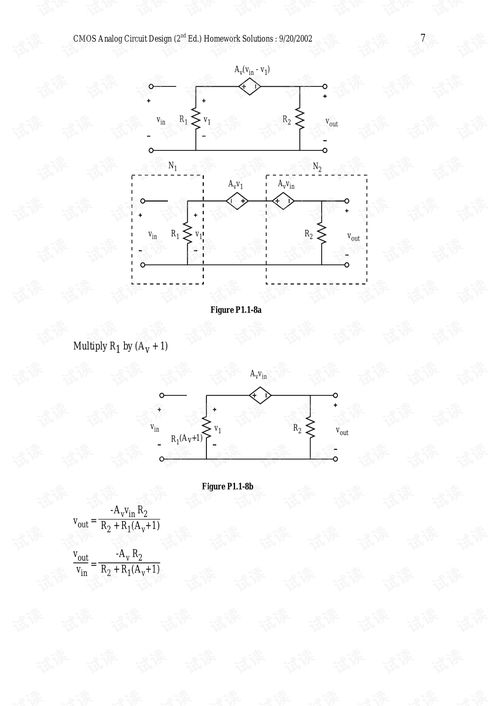

- 线性区与饱和区:在模拟电路中,放大器、电流镜等核心模块的设计高度依赖于将MOS偏置在饱和区以获得高增益和良好电流复制;而线性区则用于实现开关、电阻等无源功能。

三、非理想效应与设计模型的演进

理想的平方律模型已无法精确描述纳米级MOS的行为。设计中必须考虑:

- 沟道长度调制效应:导致饱和区输出电阻有限,影响运算放大器的增益和电流镜的匹配精度,设计中需采用共源共栅等结构进行补偿。

- 体效应:源-衬底电压变化引起阈值电压漂移,在模拟电路(如低压差分放大器)和数字电路(如传输门)中必须予以考虑。

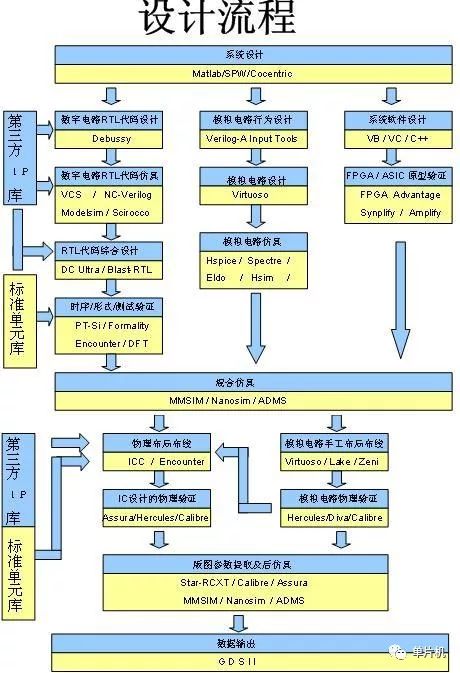

- 高级模型的应用:BSIM等基于物理的精密模型被集成到SPICE等仿真工具中,使设计师能在电路设计阶段更准确地预测性能,进行功耗、速度和面积的折衷。

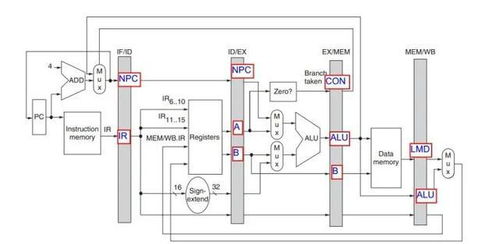

四、互连与器件协同设计

在超大规模集成电路中,由铜/低k介质构成的互连线产生的电阻、电容和电感效应,其影响已与晶体管本身性能同等重要。互连延迟可能超过门延迟,成为关键路径的决定因素。这要求:

- 物理设计阶段必须进行精细的布线规划、插入缓冲器、优化时钟树。

- 从系统架构上,采用网络化、模块化的设计(如片上网络)来应对全局互连的挑战。

五、新结构器件与设计范式的拓展

为应对传统平面MOS的物理极限,新结构器件如FinFET、全环绕栅极晶体管已进入量产。这些器件具有更好的栅控能力和更低的漏电,但同时也带来了新的设计考量:

- 三维结构引入了新的寄生参数和制造变异。

- 设计工具和库需要更新以支持新器件的独特特性。

- 为充分发挥其性能优势,可能需要探索新的电路架构和设计方法。

###

MOS器件原理不仅是半导体物理的课题,更是超大规模集成电路设计的底层语言。从微缩定律到非理想效应,从工作区域到新型结构,器件的每一个物理特性都在芯片的设计规则、性能优化、功耗管理和可靠性保障中留下了深刻的烙印。理解并驾驭这些原理,是连接晶体管与复杂系统,成功设计出高效、可靠超大规模集成电路的必经之路。随着器件技术继续向原子尺度演进,这一协同设计与创新的过程必将更加紧密和富有挑战性。

如若转载,请注明出处:http://www.kclgames.com/product/67.html

更新时间:2026-02-24 20:14:58